Menu

- 8 Bit 2 To 1 Multiplexer Verilog Code

- 8 To 1 Multiplexer Vhdl

- 8 To 1 Multiplexer Circuit Diagram

- 8 1 Multiplexer Truth Table

- 8 Bit 4 To 1 Mux Verilog

- Verilog Code For 8 To 1 Multiplexer Using Dataflow Modelling

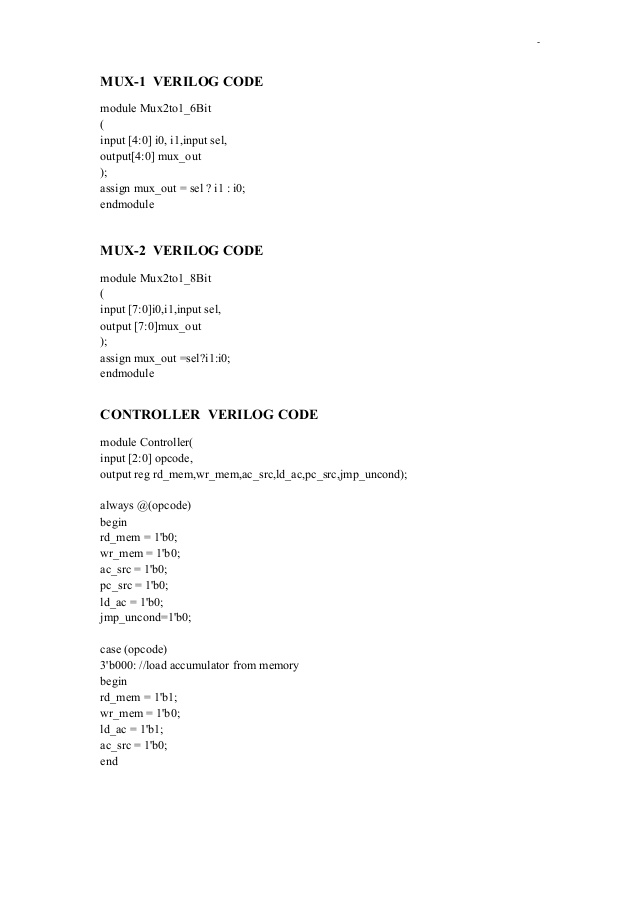

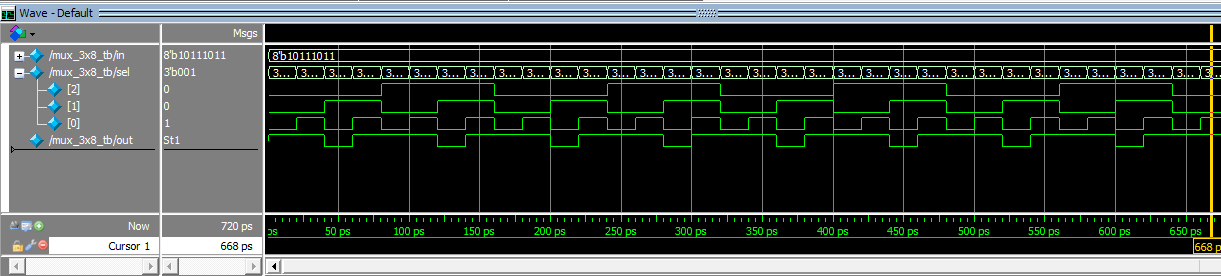

4 to 1 Multiplexer Design using Logical Expression (Verilog CODE) 4 to 1 Multiplexer Design using Logical Expression (Data Flow Modeling Style)- Output Waveform: 4 to 1 Multiplexer Program.

Question: Implement 8 To 1 Multiplexer Using Verilog. Both In Structural And Behavioral And Test Bench. This problem has been solved! See the answer. A multiplexer is a device that selects one of several input signals and forwards the selected input to the output. Typical multiplexers come in 2:1, 4:1, 8:1, and 16:1 forms. A multiplexer of 2n inputs has n select lines. A TTL series 8:1 MUX is 74151. It has three select lines S2, S1, S0. Each of the 8.

a multiplexer (or MUX) is a device that selects one of several analog or digital input signals and forwards the selected input into a single line. A multiplexer of 2n inputs has n select lines, which are used to select which input line to send to the output. Multiplexers are mainly used to increase the amount of data that can be sent over the network within a certain amount of time and bandwidth. A multiplexer is also called a data selector. They are used in CCTV, and almost every business that has CCTV fitted, will own one of these.

Active4 years, 4 months ago

I am trying to create a 8 x 1 multiplexer in Verilog. When I run analysis and synthesis the code I keep getting an error. Here is my code:

Here is the error message:

Error (10170): Verilog HDL syntax error at KuchtaClayton_HW7_P6.v(6) near text 'â'; expecting ')'

There are 21 errors that are essentially the same, some look like this:

8 Bit 2 To 1 Multiplexer Verilog Code

Error (10170): Verilog HDL syntax error at KuchtaClayton_HW7_P6.v(6) near text â

Error (10170): Verilog HDL syntax error at KuchtaClayton_HW7_P6.v(6) near text

Error (10170): Verilog HDL syntax error at KuchtaClayton_HW7_P6.v(6) near text

I double click on them and they bring me to each assign line for Y 3 times. I am guessing I did three errors in each Boolean expression? What am I doing wrong in the assign? I am using Quartus II as my program.

8 To 1 Multiplexer Vhdl

Qiu4,2791010 gold badges3838 silver badges5050 bronze badges

user1334858user13348588 To 1 Multiplexer Circuit Diagram

8 1 Multiplexer Truth Table

74944 gold badges1919 silver badges3636 bronze badges

8 Bit 4 To 1 Mux Verilog

1 Answer

Verilog Code For 8 To 1 Multiplexer Using Dataflow Modelling

I can only guess how on earth have you ended up with

’ character in your code as it is not that easy to type in (i.e. on Mac you have to hold Shift+Option+]). At any rate, that character is a Unicode 0xE28099 and is not a legal Verilog code. You are expected to use ASCII character ', which is 0x07 (see a table of ASCII characters). Other than that, your syntax is OK. The only suggestion is not to use

1'bx there because with 3 bits you can represent up to 8 numbers (from 0 to 7) and thus you have a full case, so that the following code can be used: user405725